# www.DataSheet4U.com

# **HN27C4000G Series**

524288-Word × 8-Bit/262144-Word × 16-Bit CMOS UV Erasable and Programmable ROM

# **HITACHI**

Rev. 1 Nov. 10, 1994

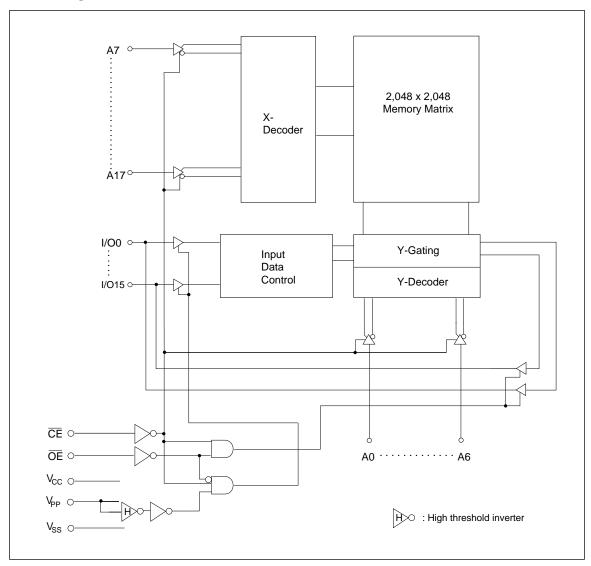

The Hitachi HN27C4000 is a 4-Mbit UV erasable and electrically programmable ROM that is organized either as 524288-word × 8 bit or as 262144-word × 16 bit, featuring extra-high speed burst mode that gives two times faster 4-word or 8-byte serial access than normal. And also high speed and fast programming are served as well as the existing Hitachi 4M device HN27C4096 and HN27C4001. Fabricated on advanced fine process and high speed circuitry technique, HN27C4000 makes high speed access time and low power dissipation in either active or stand-by mode. Therefore, it is suitable for all systems featuring high speed microprocessor such as the 80386, 80486, 68030, 68040 and so on.

#### **Features**

- Organization: 524288-word × 8-bit/262144word × 16-bit (BYTE /Vpp enables selection byte-wide or word-wide)

- High speed: Access time 100 ns/120 ns/150 ns (max)

Burst access time 50 ns/60 ns/60 ns (max)

- Low power dissipation:

Standby mode; 5 μW (typ),

Active mode; 150 mW/MHz (typ)

- Fast high reliability page programming, fast high-reliability programming and option programming: Program voltage; +12.5 V DC

Program time; 3.5 sec (min)

(Theoretical in Page)

(Theoretical in Page programming)

- Inputs and outputs TTL compatible during both read and program modes

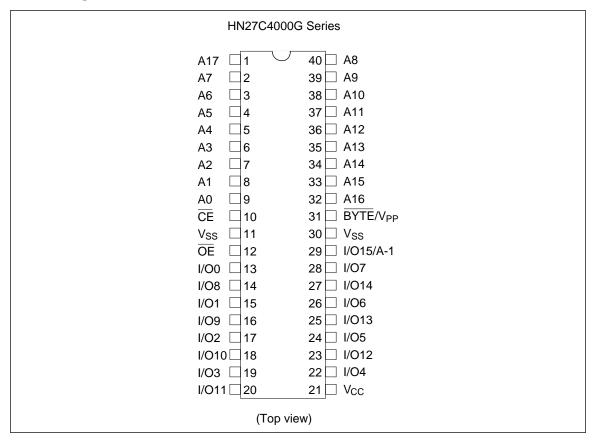

- Pin arrangement: 40-pin EIAJ standard pin compatible with HN62414/ HN62434

- Device identifier mode: Manufacturer code and device code

#### **Pin Arrangement**

#### **Ordering Information**

| Type No.      | Access time | Package       |

|---------------|-------------|---------------|

| HN27C4000G-10 | 100 ns      | 600-mil       |

| HN27C4000G-12 | 120 ns      | 40-pin cerdip |

| HN27C4000G-15 | 150 ns      | <br>(DG-40A)  |

#### **Pin Description**

| Pin name             | Function                                         |

|----------------------|--------------------------------------------------|

| A0 – A17             | Address                                          |

| I/O0 – I/O14         | Input/output                                     |

| I/O15/A-1            | Input/output/address                             |

| CE                   | Chip enable                                      |

| ŌĒ                   | Output enable                                    |

| V <sub>CC</sub>      | Power supply                                     |

| BYTE/V <sub>PP</sub> | Byte/word selection/<br>Programming power supply |

| V <sub>SS</sub>      | Ground                                           |

# **Block Diagram**

#### **Mode Selection**

|                   | Pin      | CE              | OE              | Α9   | BYTE/V <sub>PP</sub> | $v_{cc}$        | I/O0 – I/O7, I/O8 – I/O14, I/O15/A |          | 4, I/O15/A-1                     |

|-------------------|----------|-----------------|-----------------|------|----------------------|-----------------|------------------------------------|----------|----------------------------------|

| Mode              | DG-40A   | (10)            | (12)            | (39) | (31)                 | (21)            | (13 – 20,                          | 22 – 28, | 29)                              |

| Read (X16 bit)    |          | $V_{IL}$        | $V_{IL}$        | Χ    | $V_{IH}$             | V <sub>CC</sub> | Dout                               | Dout     | Dout                             |

| Read (X8 bit)     |          | $V_{IL}$        | $V_{IL}$        | Χ    | $V_{IL}$             | $V_{CC}$        | Dout                               | High-Z   | V <sub>IH</sub> /V <sub>IL</sub> |

| Output disable (2 | X16 bit) | $V_{IL}$        | $V_{IH}$        | Χ    | $V_{IH}$             | $V_{CC}$        | High-Z                             | High-Z   | High-Z                           |

| Output disable (2 | X8 bit)  | V <sub>IL</sub> | V <sub>IH</sub> | Χ    | V <sub>IL</sub>      | Vcc             | High-Z                             | High-Z   | V <sub>IH</sub> /V <sub>IL</sub> |

# Mode Selection (cont)

|         | Pin                 | CE                | OE         | A9         | BYTE/V <sub>PP</sub>              | $v_{cc}$        | 1/00 – 1/07 | , I/O8 – I/O14 | , I/O15/A-1 |

|---------|---------------------|-------------------|------------|------------|-----------------------------------|-----------------|-------------|----------------|-------------|

| Mode    | DG-40A              | (10)              | (12)       | (39)       | (31)                              | (21)            | (13 – 20,   | 22 – 28,       | 29)         |

| Stand   | by                  | $V_{IH}$          | Χ          | Χ          | V <sub>SS</sub> – V <sub>CC</sub> | V <sub>CC</sub> | High-Z      | High-Z         | High-Z      |

| Page    | Page program set    | $V_{IH}$          | $V_H^{*2}$ | Χ          | $V_{PP}$                          | $V_{CC}$        | High-Z      | High-Z         | High-Z      |

| prog.   | Page data latch     | $V_{IL}$          | $V_H^{*2}$ | Χ          | $V_{PP}$                          | $V_{CC}$        | Din         | Din            | Din         |

|         | Page program        | $V_{IL}$          | $V_{IH}$   | Χ          | $V_{PP}$                          | $V_{CC}$        | High-Z      | High-Z         | High-Z      |

|         | Page program verify | v V <sub>IH</sub> | $V_{IL}$   | Χ          | $V_{PP}$                          | $V_{CC}$        | Dout        | Dout           | Dout        |

|         | Page program reset  | V <sub>IH</sub>   | $V_{IH}$   | Χ          | V <sub>CC</sub>                   | $V_{CC}$        | High-Z      | High-Z         | High-Z      |

| Word    | Program             | $V_{IL}$          | $V_{IH}$   | Χ          | $V_{PP}$                          | $V_{CC}$        | Din         | Din            | Din         |

| prog.   | Program verify      | $V_{IH}$          | $V_{IL}$   | Χ          | $V_{PP}$                          | $V_{CC}$        | Dout        | Dout           | Dout        |

|         | Optional verify     | $V_{IL}$          | $V_{IL}$   | Χ          | $V_{PP}$                          | $V_{CC}$        | Dout        | Dout           | Dout        |

|         | Program inhibit     | $V_{IH}$          | $V_{IH}$   | Χ          | $V_{PP}$                          | $V_{CC}$        | High-Z      | High-Z         | High-Z      |

| Identif | fier                | $V_{IL}$          | $V_{IL}$   | $V_H^{*2}$ | $V_{SS} - V_{CC}$                 | $V_{CC}$        | Code        | Code           | Code        |

Notes: 1. X: Don't care.

2.  $V_H$ : 12.0  $V \pm 0.5 V$

# **Absolute Maximum Ratings**

| Item                            | Symbol          | Value                | Unit |

|---------------------------------|-----------------|----------------------|------|

| All input and output voltages*1 | Vin, Vout       | $-0.6^{*2}$ to +7.0  | V    |

| Voltage on pin A9 and OE        | $V_{ID}$        | $-0.6^{*2}$ to +13.0 | V    |

| V <sub>PP</sub> voltage *1      | $V_{PP}$        | -0.6 to +13.5        | V    |

| V <sub>CC</sub> voltage *1      | V <sub>CC</sub> | -0.6 to +7.0         | V    |

| Operating temperature range     | Topr            | 0 to +70             | °C   |

| Storage temperature range *3    | Tstg            | -65 to +125          | °C   |

| Storage temperature under bias  | Tbias           | -20 to +80           | °C   |

Notes: 1. Relative to  $V_{SS}$ .

- 2. Vin, Vout,  $V_{ID}$  min = -2.0 V for pulse width  $\leq$  20 ns

- 3. Storage temperature range of device before programming.

#### **Capacitance** (Ta = $25^{\circ}$ C, f = 1 MHz)

| Item               | Symbol | Min | Тур | Max | Unit | Test conditions | Notes                       |

|--------------------|--------|-----|-----|-----|------|-----------------|-----------------------------|

| Input capacitance  | Cin    | _   | _   | 12  | pF   | Vin = 0 V       | Except BYTE/V <sub>PP</sub> |

| Output capacitance | Cout   | _   | _   | 20  | pF   | Vout = 0 V      |                             |

#### **Read Operation**

**DC Characteristics** ( $V_{CC}$  = 5 V  $\pm$  10%,  $V_{PP}$  =  $V_{SS}$  to  $V_{CC}$ , Ta = 0 to  $+70^{\circ}C$ )

| Item                              | Symbol           | Min                | Тур | Max                      | Unit | Test conditions                                          |

|-----------------------------------|------------------|--------------------|-----|--------------------------|------|----------------------------------------------------------|

| Input leakage current             | ILI              | _                  | _   | 2                        | μΑ   | Vin = 5.5 V                                              |

| Output leakage current            | $I_{LO}$         | _                  | _   | 2                        | μΑ   | Vout = 5.5 V/0.45 V                                      |

| V <sub>PP</sub> current           | I <sub>PP1</sub> | _                  | 1   | 20                       | μΑ   | V <sub>PP</sub> = 5.5 V                                  |

| Standby V <sub>CC</sub> current   | I <sub>SB1</sub> | _                  | _   | 1                        | mA   | CE = V <sub>IH</sub>                                     |

|                                   | I <sub>SB2</sub> | _                  | 1   | 20                       | μΑ   | $\overline{\text{CE}} = V_{\text{CC}} \pm 0.3 \text{ V}$ |

| Operating V <sub>CC</sub> current | I <sub>CC1</sub> | _                  | _   | 35                       | mA   | lout = 0 mA, f = 1 MHz                                   |

|                                   | I <sub>CC2</sub> | _                  | _   | 120                      | mA   | lout = 0 mA, f = 10 MHz                                  |

| Input voltage                     | $V_{IL}$         | -0.3 <sup>*1</sup> | _   | 0.8                      | V    |                                                          |

|                                   | V <sub>IH</sub>  | 2.2                | _   | V <sub>CC</sub><br>+ 1*2 | V    |                                                          |

| Output voltage                    | V <sub>OL</sub>  | _                  | _   | 0.45                     | V    | I <sub>OL</sub> = 2.1 mA                                 |

|                                   | V <sub>OH</sub>  | 2.4                | _   | _                        | V    | I <sub>OH</sub> = -400 μA                                |

Notes: 1.  $V_{IL} min = -1.0 V$  for pulse width  $\leq 50 ns$

$V_{IL}$  min = -2.0 V for pulse width  $\leq$  20 ns

2.  $V_{IH}$  max =  $V_{CC}$  +1.5 V for pulse width  $\leq$  20 ns

If  $V_{\text{IH}}$  is over the specified maximum value, read operation cannot be guaranteed.

# AC Characteristics ( $V_{CC}$ = 5 V $\pm$ 10%, $V_{PP}$ = $V_{SS}$ to $V_{CC}$ , Ta = 0 to +70°C)

#### **Test Conditions**

Input pulse levels: 0.45 to 2.4 V

Input rise and fall times: ≤ 10 ns

Output load: 1 TTL gate +100 pF

• Reference levels for measuring timing: 0.8 V, 2.0 V

|                               |                  | HN27<br>-10 | 'C4000 | HN27<br>-12 | C4000 | HN27C4000<br>-15 |     |      |                                          |

|-------------------------------|------------------|-------------|--------|-------------|-------|------------------|-----|------|------------------------------------------|

| Item                          | Symbol           | Min         | Max    | Min         | Max   | Min              | Max | Unit | Test conditions                          |

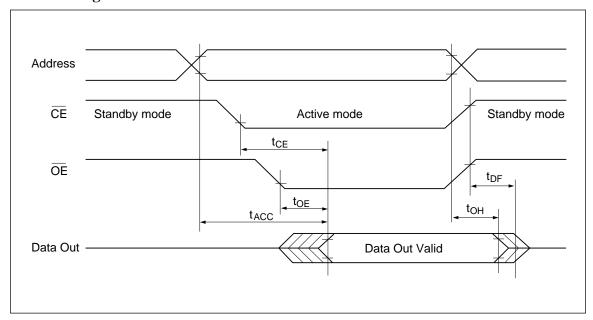

| Address to output delay       | t <sub>ACC</sub> | _           | 100    | _           | 120   | _                | 150 | ns   | $\overline{CE} = \overline{OE} = V_{IL}$ |

| CE to output delay            | t <sub>CE</sub>  | _           | 100    | _           | 120   | _                | 150 | ns   | OE = V <sub>IL</sub>                     |

| OE to output delay            | t <sub>OE</sub>  | _           | 60     | _           | 60    | _                | 70  | ns   | CE = V <sub>IL</sub>                     |

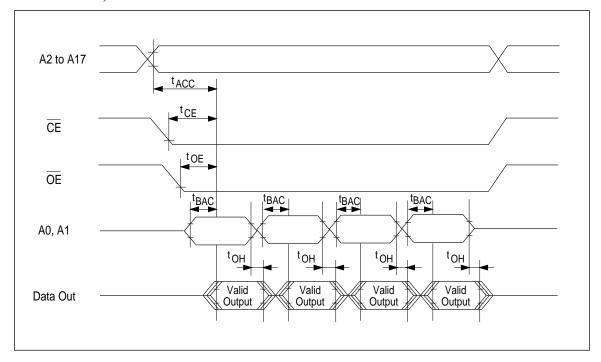

| Burst address to output delay | t <sub>BAC</sub> | _           | 50     | -           | 60    | _                | 60  | ns   | CE = V <sub>IL</sub>                     |

| OE high to output float *1    | t <sub>DF</sub>  | 0           | 35     | 0           | 40    | 0                | 50  | ns   | CE = V <sub>IL</sub>                     |

| Address to output hold        | t <sub>OH</sub>  | 5           |        | 5           | _     | 5                | _   | ns   | $\overline{CE} = \overline{OE} = V_{IL}$ |

Note: 1. t<sub>DF</sub> is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

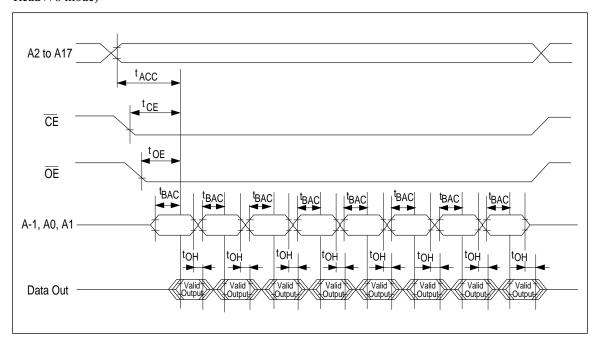

#### **Read Timing Waveform**

# Read Timing Waveform (Burst access mode)

In Burst Access mode, fast read-out of 4 word data is selected by address A0, A1. (Valid only for Read  $\times$  16 mode)

In Burst Access mode, fast read-out of 8 byte data is selected by address A-1, A0, A1. (Valid only for Read  $\times$  8 mode)

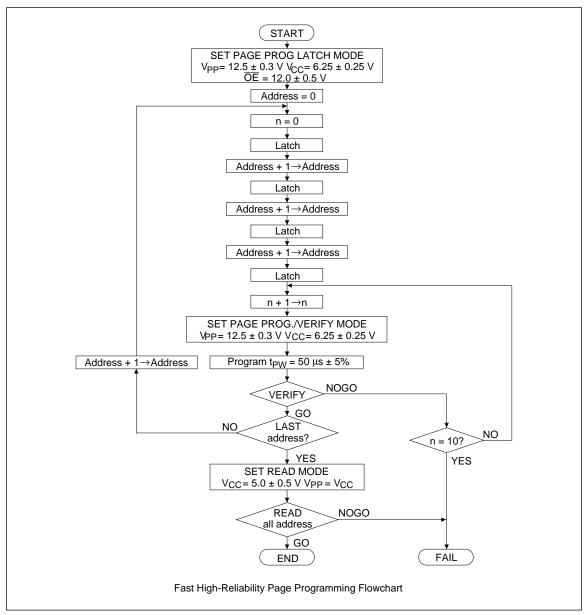

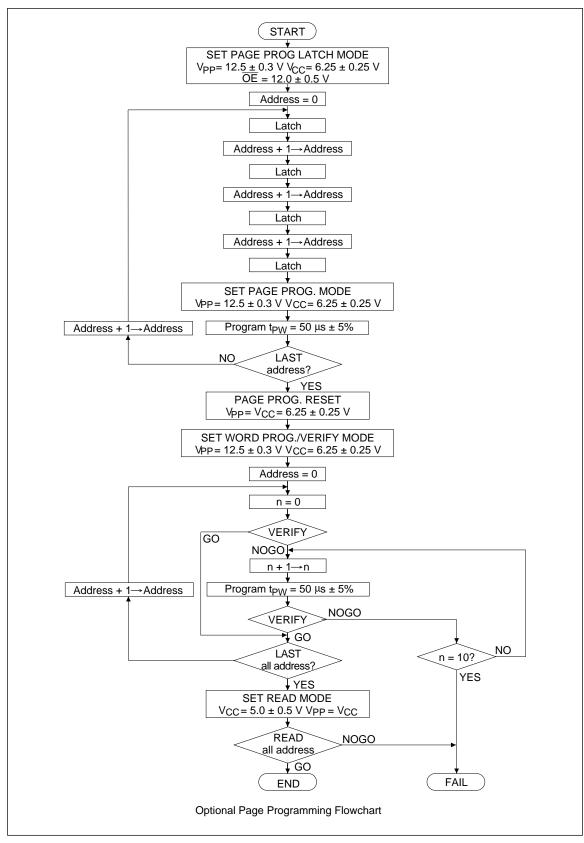

# Fast High-Reliability Page Programming

This device can be applied the high performance page programming algorithm shown in the following flowchart. This algorithm allows to obtain faster programming time without any voltage stress to the device nor deterioration in reliability of programmed data.

#### Page Program Set

Apply 12 V to  $\overline{OE}$  pin after applying 12.5 V to V<sub>PP</sub> to set a page program mode.

The device operates in a page program mode until reset.

#### **Page Program Reset**

Set  $V_{PP}$  to  $V_{CC}$  level or less to reset a page program mode.

**DC Characteristics** (

$$V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}$$

,  $V_{PP} = 12.5 \text{ V} \pm 0.3 \text{ V}$ ,  $Ta = 25^{\circ}\text{C} \pm 5^{\circ}\text{C}$ )

| Item                              | Symbol           | Min                | Тур  | Max                        | Unit | Test conditions           |

|-----------------------------------|------------------|--------------------|------|----------------------------|------|---------------------------|

| Input leakage current             | ILI              | _                  | _    | 2                          | μΑ   | Vin = 6.5 V/0.45 V        |

| Output voltage during verify      | $V_{OL}$         | _                  | _    | 0.45                       | V    | $I_{OL} = 2.1 \text{ mA}$ |

|                                   | V <sub>OH</sub>  | 2.4                | _    | _                          | V    | $I_{OH} = -400 \mu A$     |

| Operating V <sub>CC</sub> current | I <sub>CC</sub>  | _                  | _    | 50                         | mA   |                           |

| Input voltage                     | $V_{IL}$         | -0.1 <sup>*5</sup> | _    | 0.8                        | V    |                           |

|                                   | $V_{IH}$         | 2.2                | _    | V <sub>CC</sub><br>+ 0.5*6 | V    |                           |

|                                   | $\overline{V_H}$ | 11.5               | 12.0 | 12.5                       | V    |                           |

| V <sub>PP</sub> supply current    | I <sub>PP</sub>  | _                  | _    | 70                         | mA   | CE = V <sub>IL</sub>      |

Notes: 1. V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

- 2. V<sub>PP</sub> must not exceed 13 V including overshoot.

- 3. An influence may be had upon device reliability if the device is installed or removed while  $V_{PP} = 12.5 \text{ V}$ .

- 4. Do not alter  $V_{PP}$  either  $V_{IL}$  to 12.5 V or 12.5 V to  $V_{IL}$  when  $\overline{CE}$  = low.

- 5.  $V_{IL}$  min = -0.6 V for pulse width  $\leq$  20 ns.

- 6. If V<sub>IH</sub> is over the specified maximum value, programming operation cannot be guaranteed.

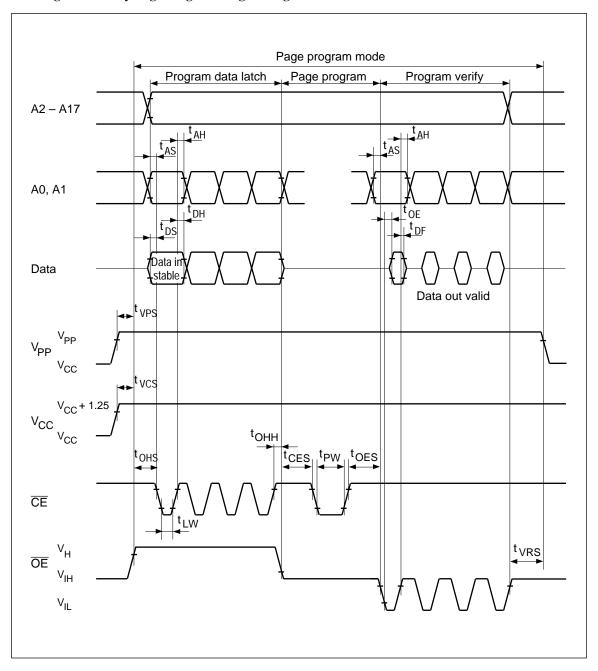

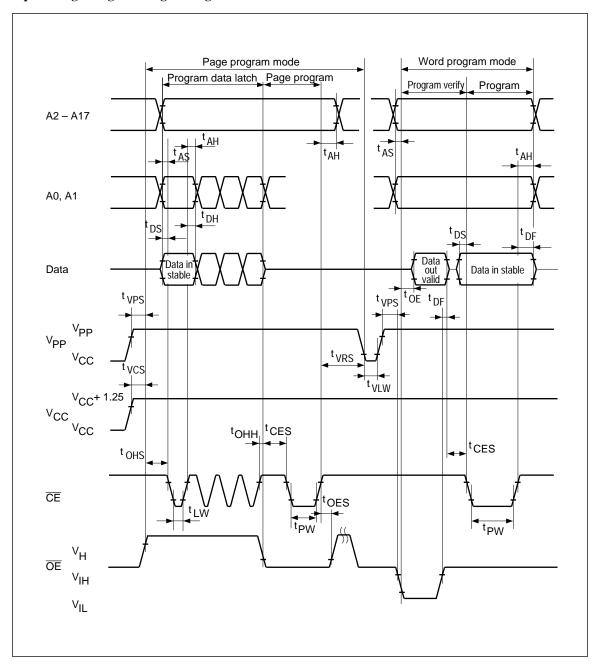

# AC Characteristics (V<sub>CC</sub> = 6.25 V $\pm$ 0.25 V, V<sub>PP</sub> = 12.5 V $\pm$ 0.3 V, Ta = 25°C $\pm$ 5°C)

#### **Test Conditions**

Input pulse levels: 0.45 to 2.4 V

Input rise and fall times: ≤ 20 ns

• Reference levels for measuring timing: Inputs; 0.8 V, 2.0 V,

Outputs; 0.8 V, 2.0 V

| Item                                    | Symbol             | Min  | Тур  | Max  | Unit | Test conditions |

|-----------------------------------------|--------------------|------|------|------|------|-----------------|

| Address setup time                      | t <sub>AS</sub>    | 2    | _    | _    | μs   |                 |

| OE setup time                           | toes               | 2    | _    | _    | μs   |                 |

| Data setup time                         | $t_{DS}$           | 2    | _    | _    | μs   |                 |

| Address hold time                       | t <sub>AH</sub>    | 0    | _    | _    | μs   |                 |

| Data hold time                          | $t_{DH}$           | 2    | _    | _    | μs   |                 |

| OE high to output float delay           | t <sub>DF</sub> *1 | 0    | _    | 130  | ns   |                 |

| V <sub>PP</sub> setup time              | t <sub>VPS</sub>   | 2    | _    | _    | μs   |                 |

| V <sub>CC</sub> setup time              | $t_{VCS}$          | 2    | _    | _    | μs   |                 |

| CE initial programming pulse width      | t <sub>PW</sub>    | 47.5 | 50.0 | 52.5 | μs   |                 |

| CE setup time                           | t <sub>CES</sub>   | 2    | _    | _    | μs   |                 |

| Data valid from OE                      | t <sub>OE</sub>    | 0    | _    | 150  | ns   |                 |

| CE pulse width during data latch        | t <sub>LW</sub>    | 1    | _    | _    | μs   |                 |

| OE = V <sub>H</sub> setup time          | tons               | 2    | _    | _    | μs   |                 |

| OE = V <sub>H</sub> hold time           | t <sub>OHH</sub>   | 2    | _    | _    | μs   |                 |

| V <sub>PP</sub> hold time <sup>*2</sup> | t <sub>VRS</sub>   | 1    | _    | _    | μs   |                 |

Notes: 1. t<sub>DF</sub> is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

2. Page program mode will be reset when  $V_{\mbox{\footnotesize{PP}}}$  is set to  $V_{\mbox{\footnotesize{CC}}}$  or less.

# Fast High-Reliability Page Programming Timing Waveform

#### **Fast High-Reliability Programming**

This device can be applied the fast high-reliability programming algorithm shown in the following flowchart. This algorithm allows to obtain faster programming time without any voltage stress to the device nor deterioration in reliability of programmed data.

**DC Characteristics** ( $V_{CC}$  = 6.25 V  $\pm$  0.25 V,  $V_{PP}$  =12.5 V  $\pm$  0.3 V, Ta=25°C  $\pm$  5°C)

| Item                              | Symbol            | Min                | Тур | Max                        | Unit | <b>Test conditions</b>    |

|-----------------------------------|-------------------|--------------------|-----|----------------------------|------|---------------------------|

| Input leakage current             | ILI               | _                  | _   | 2                          | μΑ   | Vin = 6.5 V/0.45 V        |

| V <sub>PP</sub> supply current    | I <sub>PP</sub>   | _                  | _   | 40                         | mA   | CE = V <sub>IL</sub>      |

| Operating V <sub>CC</sub> current | Icc               | _                  | _   | 50                         | mA   |                           |

| Input voltage                     | V <sub>IL</sub>   | -0.1 <sup>*5</sup> | _   | 0.8                        | V    |                           |

|                                   | $\overline{V_IH}$ | 2.2                | _   | V <sub>CC</sub><br>+ 0.5*6 | V    |                           |

| Output voltage                    | V <sub>OL</sub>   | _                  | _   | 0.45                       | V    | I <sub>OL</sub> = 2.1 mA  |

|                                   | V <sub>OH</sub>   | 2.4                | _   | _                          | V    | I <sub>OH</sub> = -400 μA |

Notes: 1. V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

- 2. V<sub>PP</sub> must not exceed 13 V including overshoot.

- 3. An influence may be had upon device reliability if the device is installed or removed while  $V_{PP} = 12.5 \text{ V}$ .

- 4. Do not alter  $V_{PP}$  either  $V_{IL}$  to 12.5 V or 12.5 V to  $V_{IL}$  when  $\overline{CE}$  = low.

- 5.  $V_{IL}$  min = -0.6 V for pulse width  $\leq$  20 ns.

- 6. If V<sub>IH</sub> is over the specified maximum value, programming operation cannot be guaranteed.

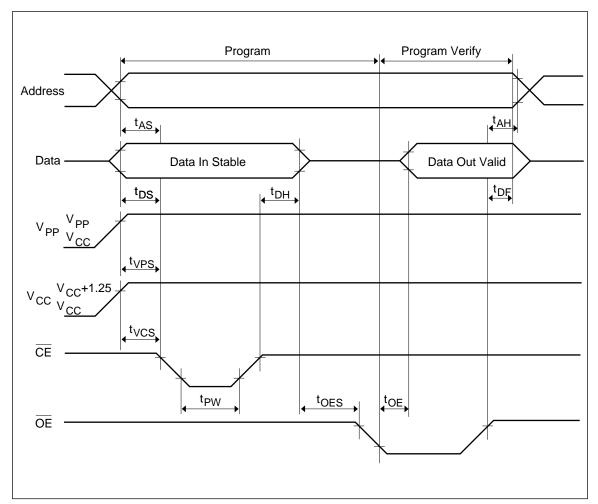

AC Characteristics ( $V_{CC}$  = 6.25 V  $\pm$  0.25 V,  $V_{PP}$  = 12.5 V  $\pm$  0.3 V, Ta = 25°C  $\pm$  5°C)

#### **Test Conditions**

Input pulse levels: 0.45 to 2.4 V

Input rise and fall times: ≤ 20 ns

• Reference levels for measuring timings: 0.8 V, 2.0 V

| Item                               | Symbol             | Min  | Тур  | Max  | Unit | Test conditions |

|------------------------------------|--------------------|------|------|------|------|-----------------|

| Address setup time                 | t <sub>AS</sub>    | 2    | _    | _    | μs   |                 |

| OE setup time                      | toes               | 2    | _    | _    | μs   |                 |

| Data setup time                    | t <sub>DS</sub>    | 2    | _    | _    | μs   |                 |

| Address hold time                  | t <sub>AH</sub>    | 0    | _    | _    | μs   |                 |

| Data hold time                     | t <sub>DH</sub>    | 2    | _    | _    | μs   |                 |

| OE to output float delay           | t <sub>DF</sub> *1 | 0    | _    | 130  | ns   |                 |

| V <sub>PP</sub> setup time         | t <sub>VPS</sub>   | 2    | _    | _    | μs   |                 |

| V <sub>CC</sub> setup time         | t <sub>VCS</sub>   | 2    | _    | _    | μs   |                 |

| CE initial programming pulse width | t <sub>PW</sub>    | 47.5 | 50.0 | 52.5 | μs   |                 |

| Data valid from OE                 | t <sub>OE</sub>    | 0    | _    | 150  | ns   |                 |

Note: 1. t<sub>DF</sub> is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

#### Fast High-Reliability Programming Timing Waveform

#### **Optional Page Programming**

This device can be applied the optional page programming algorithm shown in the following flowchart. This algorithm allows to obtain faster programming time without any voltage stress to the device nor deterioration in reliability of programmed data.

This programming algorithm is the combination of page programming and word verify. It can avoid the increase of programming verify time when a programmer with slow machine cycle is used, and shorten the total programming time.

Regarding the timing specifications for page programming and word verify, please refer to the specifications for fast high-reliability page programming and fast high-reliability programming.

DC Characteristics (V<sub>CC</sub> = 6.25 V  $\pm$  0.25 V, V<sub>PP</sub> =12.5 V  $\pm$  0.3 V, Ta = 25°C  $\pm$  5°C)

| Item                              | Symbol           | Min                | Тур  | Max                                    | Unit | Test conditions          |

|-----------------------------------|------------------|--------------------|------|----------------------------------------|------|--------------------------|

| Input leakage current             | ILI              | _                  | _    | 2                                      | μΑ   | Vin = 6.5 V/0.45 V       |

| Output voltage during verify      | $V_{OL}$         | _                  | _    | 0.45                                   | V    | I <sub>OL</sub> = 2.1 mA |

|                                   | V <sub>OH</sub>  | 2.4                | _    | _                                      | V    | $I_{OH} = -400 \ \mu A$  |

| Operating V <sub>CC</sub> current | I <sub>CC</sub>  | _                  | _    | 50                                     | mA   |                          |

| Input voltage                     | $V_{IL}$         | -0.1 <sup>*5</sup> | _    | 0.8                                    | V    |                          |

|                                   | $V_{IH}$         | 2.2                | _    | V <sub>CC</sub><br>+ 0.5 <sup>*6</sup> | V    |                          |

|                                   | $\overline{V_H}$ | 11.5               | 12.0 | 12.5                                   | V    |                          |

| V <sub>PP</sub> supply current    | I <sub>PP</sub>  | _                  | _    | 70                                     | mA   | CE = V <sub>IL</sub>     |

Notes: 1.  $V_{CC}$  must be applied simultaneously or before  $V_{PP}$  and removed simultaneously or after  $V_{PP}$ .

- 2. V<sub>PP</sub> must not exceed 13 V including overshoot.

- 3. An influence may be had upon device reliability if the device is installed or removed while  $V_{PP} = 12.5 \text{ V}$ .

- 4. Do not alter  $V_{PP}$  either  $V_{IL}$  to 12.5 V or 12.5 V to  $V_{IL}$  when  $\overline{CE}$  = low.

- 5.  $V_{IL}$  min = -0.6 V for pulse width  $\leq$  20 ns.

- 6. If  $V_{\text{IH}}$  is over the specified maximum value, programming operation cannot be guaranteed.

AC Characteristics ( $V_{CC}$  = 6.25 V  $\pm$  0.25 V,  $V_{PP}$  = 12.5 V  $\pm$  0.3 V, Ta = 25°C  $\pm$  5°C)

#### **Test Conditions**

Input pulse levels: 0.45 to 2.4 V

Input rise and fall times: ≤ 20 ns

$\bullet$  Reference levels for measuring timings: Inputs;  $~0.8~V,\,2.0~V$

Outputs; 0.8 V, 2.0 V

| Item                               | Symbol             | Min  | Тур  | Max  | Unit | Test conditions |

|------------------------------------|--------------------|------|------|------|------|-----------------|

| Address setup time                 | t <sub>AS</sub>    | 2    | _    | _    | μs   |                 |

| OE setup time                      | t <sub>OES</sub>   | 2    | _    | _    | μs   |                 |

| Data setup time                    | t <sub>DS</sub>    | 2    | _    | _    | μs   |                 |

| Address hold time                  | t <sub>AH</sub>    | 0    | _    | _    | μs   |                 |

| Data hold time                     | t <sub>DH</sub>    | 2    | _    | _    | μs   |                 |

| OE high to output float delay      | t <sub>DF</sub> *1 | 0    | _    | 130  | ns   |                 |

| V <sub>PP</sub> setup time         | t <sub>VPS</sub>   | 2    | _    | _    | μs   |                 |

| V <sub>CC</sub> setup time         | $t_{VCS}$          | 2    | _    | _    | μs   |                 |

| CE initial programming pulse width | t <sub>PW</sub>    | 47.5 | 50.0 | 52.5 | μs   |                 |

| CE setup time                      | t <sub>CES</sub>   | 2    | _    | _    | μs   |                 |

| Data valid from OE                 | t <sub>OE</sub>    | 0    | _    | 150  | ns   |                 |

| CE pulse width during data latch   | $t_{LW}$           | 1    | _    | _    | μs   |                 |

| OE = V <sub>H</sub> setup time     | t <sub>OHS</sub>   | 2    | _    | _    | μs   |                 |

| OE = V <sub>H</sub> hold time      | t <sub>OHH</sub>   | 2    | _    | _    | μs   |                 |

| Page programming reset time *2     | $t_{VLW}$          | 1    | _    | _    | μs   |                 |

| V <sub>PP</sub> hold time *2       | t <sub>VRS</sub>   | 1    | _    | _    | μs   |                 |

Notes: 1. t<sub>DF</sub> is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

2. Page program mode will be reset when  $V_{\mbox{\footnotesize{PP}}}$  is set to  $V_{\mbox{\footnotesize{CC}}}$  or less.

#### **Option Page Programming Timing Waveform**

#### **Erase**

Erasure of this device is performed by exposure to ultraviolet light of 2537 Å and all the output data are changed to "1" after this erasure procedure. The minimum integrated dose (i.e. UV intensity X exposure time) for erasure is 15 W-sec/cm<sup>2</sup>.

#### **Mode Description**

#### **Device Identifier Mode**

The device identifier mode allows the reading out of binary codes that identify manufacturer and type of device, from outputs of EPROM. By this mode, the device will be automatically matched its own corresponding programming algorithm, using programming equipment.

#### HN27C4000G Identifier Code

|             |         | A0       | I/O8 – I/O15 | I/O7 | 1/06 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | I/O0 | _ Hex |

|-------------|---------|----------|--------------|------|------|------|------|------|------|------|------|-------|

| Identifier  | DG-40   |          |              | (28) | (26) | (24) | (22) |      | (17) |      | (13) | Data  |

| Manufacture | er code | $V_{IL}$ | Х            | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 07    |

| Device code | )       | $V_{IH}$ | Χ            | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | A1    |

Notes: 1.  $V_{CC} = 5.0 \text{ V} \pm 10\%$

- 2.  $A9 = 12.0 \text{ V} \pm 0.5 \text{ V}$

- 3.  $\overline{CE}$ ,  $\overline{OE} = V_{IL}$

- 4. A1 A8, A10 A17: Don't care.

- 5. X: Don't care.